# **MOS Transistor**

#### **CHAPTER OBJECTIVES**

This chapter provides a comprehensive introduction to the modern MOSFETs in their on state. (The off state theory is the subject of the next chapter.) It covers the topics of surface mobility, body effect, a simple IV theory, and a more complete theory applicable to both long- and short-channel MOSFETs. It introduces the general concept of CMOS circuit speed and power consumption, voltage gain, high-frequency operation, and topics important to analog circuit designs such as voltage gain and noise. The chapter ends with discussions of DRAM, SRAM, and flash nonvolatile memory cells.

he **MOSFET** is by far the most prevalent semiconductor device in ICs. It is the basic building block of digital, analog, and memory circuits. Its small size allows the making of inexpensive and dense circuits such as giga-bit (Gb) memory chips. Its low power and high speed make possible chips for gigahertz (GHz) computer processors and radio-frequency (RF) cellular phones.

### 6.1 • INTRODUCTION TO THE MOSFET •

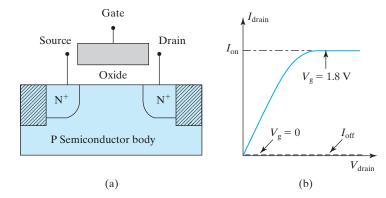

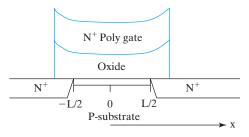

Figure 6–1 shows the basic structure of a MOSFET. The two PN junctions are the **source** and the **drain** that supplies the electrons or holes to the transistor and drains them away respectively. The name **field-effect transistor** or **FET** refers to the fact that the gate turns the transistor (inversion layer) on and off with an electric *field* through the oxide. A **transistor** is a device that presents a high input resistance to the signal source, drawing little input power, and a low resistance to the output circuit, capable of supplying a large current to drive the circuit load. The hatched regions in Fig. 6–1a are the **shallow-trench-isolation** oxide region. The silicon surfaces under the thick isolation oxide have very high threshold voltages and prevent current flows between the N<sup>+</sup> (and P<sup>+</sup>) diffusion regions along inadvertent surface inversion paths in an IC chip.

Figure 6–1 also shows the MOSFET IV characteristics. Depending on the gate voltage, the MOSFET can be off (conducting only a very small off-state leakage current,  $I_{off}$ ) or on (conducting a large on-state current,  $I_{on}$ ).

FIGURE 6-1 (a) Basic MOSFET structure and (b) IV characteristics.

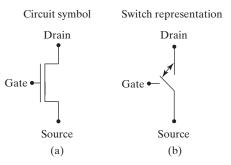

**FIGURE 6–2** Two ways of representing a MOSFET: (a) a circuit symbol and (b) as an on/off switch.

At the most basic level, a MOSFET may be thought of as an on–off switch as shown in Fig. 6–2(b). The gate voltage determines whether a current flows between the drain and source or not. The circuit symbol shown in Fig. 6–2a connotes the much more complex characteristics of the MOSFET.

### Early Patents on the FET

The transistor and IC technologies owe their success mainly to the effort and ingenuity of a large number of technologists since the mid-1900s. Two early FET patents are excerpted here. These earliest patents are presented for historical interest only. Many more conceptual and engineering innovations and efforts were required to make MOSFETs what they are today.

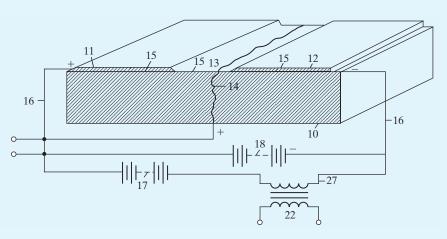

J. E. Lilienfeld's 1930 U.S. patent is considered the first teaching of the FET. In Fig. 6–3, 10 is a glass substrate while 13 is the gate electrode (in today's terminology) and "consists of an ... aluminum foil...." 11 and 12 are metal contacts to the source and drain. 15 is a thin film of semiconductor (copper sulfide). Lilienfeld taught the following novel method of making a small (short) gate, the modern photolithography technique being yet unavailable to him. The glass substrate is broken into two pieces

and then reassembled (glued back) with a thin aluminum foil inserted between the two pieces. The edge of the Al foil is used as the gate. The semiconductor film is deposited over the glass substrate and the gate, and source and drain contacts are provided. There is no oxide between the gate electrode and the semiconductor. The insulator in this FET would be the depletion layer at the metal–semiconductor junction (see Section 6.3.2).

FIGURE 6–3 "A perspective view, on a greatly enlarged scale and partly in section, of the novel apparatus as embodied by way of example in an amplifier." (From [1].)

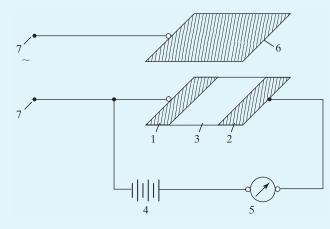

In a 1935 British patent, Oskar Heil gave a lucid description of a MOSFET. Referring to Fig. 6–4, "1 and 2 are metal electrodes between which is a thin layer 3 of semiconductor. A battery 4 sends a current through the thin layer of semiconductor and this current is measured by the ammeter 5. If, now, an electrode 6 in electro-static association with the layer 3 is charged positively or negatively in relation to the said layer 3, the electrical resistance of this layer is found to vary and the current strength as measured by the ammeter 5 also to vary."

**FIGURE 6–4** This 1935 drawing is a good illustration of a MOSFET even by today's standards. (From [2].)

#### 6.2 • COMPLEMENTARY MOS (CMOS) TECHNOLOGY •

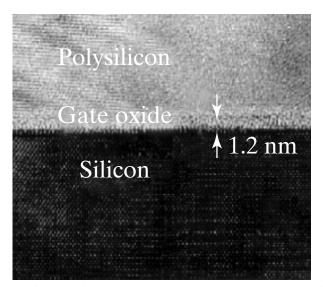

Modern MOSFET technology has advanced continually since its beginning in the 1950s. Figure 6–5 is a transmission electron microscope view of a part of a MOSFET. It shows the poly-Si gate and the single-crystalline Si body with visible individual Si atoms and a 1.2 nm amorphous  $SiO_2$  film between them. 1.2 nm is the size of four SiO<sub>2</sub> molecules.

The basic steps of fabricating the MOSFET shown in Fig. 6–1 is to first make **shallow-trench-isolation** by etching a trench that defines the boundary of the transistor and filling the trench with chemical vapor deposition (CVD) oxide (see Section 3.7.2). Next, planarize the wafer with CMP (see Section 3.8), grow a thin layer of oxide (gate oxide) over the exposed silicon surface, deposit a layer of polycrystalline silicon as the gate material (Section 3.7.2), use optical lithography to pattern a piece of photoresist, and use the photoresist as a mask to etch the poly-Si to define the gate in Fig. 6–1 (Section 3.4). Finally, implant As into the source and drain (Section 3.5.1). The implantation is masked by the gate on one side and the trench isolation on the other. Rapid thermal annealing (see text box in Section 3.6) is applied to activate the dopant and repair the implantation damage to the crystal. Contacts can then be made to the source, drain, and the gate.

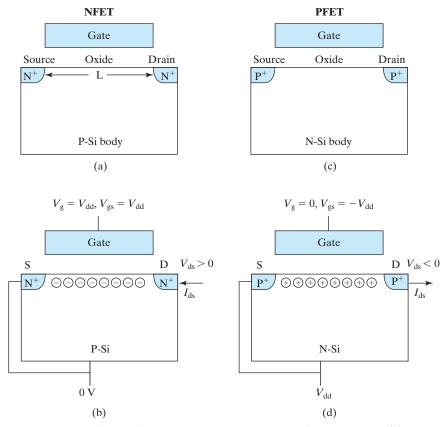

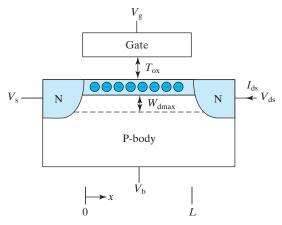

Figure 6–6a is an N-channel MOSFET, or N-MOSFET or simply NFET. It is called N-channel because the conduction channel (i.e., the inversion layer) is electron rich or N-type as shown in Fig. 6–6b. Figure 6–6c and d illustrate a **P-channel MOSFET**, or **P-MOSFET**, or **PFET**. In both cases,  $V_g$  and  $V_d$  swing between 0 V and  $V_{dd}$ , the power-supply voltage. The body of an NFET is connected to the lowest voltage in the circuit, 0 V, as shown in (b). Consequently, the PN junctions are always reverse-biased or unbiased and do not conduct forward diode current. When  $V_g$  is equal to  $V_{dd}$  as shown in (b), an inversion layer is present and the

FIGURE 6–5 Gate oxides as thin as 1.2 nm can be manufactured reproducibly. Individual Si atoms are visible in the substrate and in the polycrystalline gate. (From [3]. © 1999 IEEE.)

199

**FIGURE 6–6** Schematic drawing of an N-channel MOSFET in the off state (a) and the on state (b). (c) and (d) show a P-channel MOSFET in the off and the on states.

NFET is turned on. With its body and source connected to  $V_{dd}$ , the PFET shown in (d) responds to  $V_g$  in exactly the opposite manner. When  $V_g = V_{dd}$ , the NFET is on and the PFET is off. When  $V_g = 0$ , the PFET is on and the NFET is off.

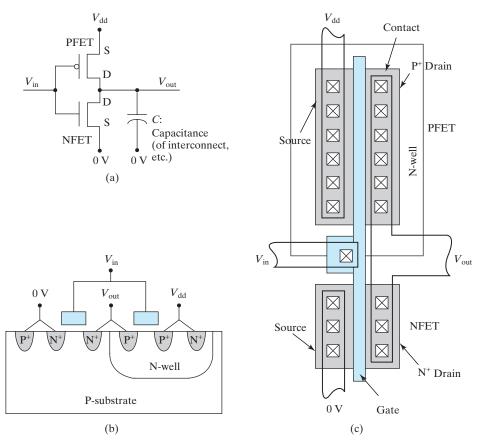

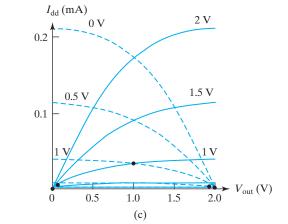

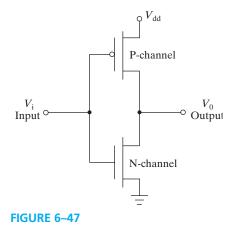

The complementary nature of NFETs and PFETs makes it possible to design low-power circuits called **CMOS** or **complementary MOS** circuits as illustrated in Fig. 6–7a. The circuit symbol of PFET has a circle attached to the gate. The example is an inverter. It charges and discharges the output node with its load capacitance, C, to either  $V_{dd}$  or 0 under the command of  $V_g$ . When  $V_g = V_{dd}$ , the NFET is on and the PFET is off (think of them as simple on–off switches), and the output node is pulled down to the ground ( $V_{out} = 0$ ). When  $V_g = 0$ , the NFET is off and the PFET is on; the output node is pulled up to  $V_{dd}$ . In either static case, one of the two transistors is off and there is no current flow from  $V_{dd}$  through the two transistors directly to the ground. Therefore, CMOS circuits consume much less power than other types of circuits. Figure 6–7b illustrates how NFET and PFET can be fabricated on the same chip. Portions of the P-type substrate are converted into N-type wells by donor implantation and diffusion. Contacts to the P substrate and N well are included in the figure. Figure 6–7c illustrates the basic **layout** of a CMOS

#### 200

Chapter 6

MOS Transistor

**FIGURE 6–7** Three views of a CMOS inverter. (a) A CMOS inverter consists of a PFET **pull-up device** and an NFET **pull-down device**. (b) Integration of NFET and PFET on the same chip. For simplicity, trench isolation (see Fig. 6–1), which fills all the surface area except for the diffusion regions and the channel regions, is not shown. (c) Layout of a CMOS inverter.

inverter. It is a view of the circuit from above the Si wafer and may be thought of as a composite drawing of several photomasks used to fabricate the inverter.  $V_{\rm in}$ ,  $V_{\rm out}$ ,  $V_{\rm dd}$ , and ground voltage are carried by metal lines. The poly-Si gate is the vertical bar connected to  $V_{\rm in}$ . The metal to semiconductor contacts are usually made in multiple identical holes because it is more difficult to fabricate contact holes of varying sizes and shapes.

### 6.3 • SURFACE MOBILITIES AND HIGH-MOBILITY FETS •

It is highly desirable to have a large transistor current so that the MOSFET can charge and discharge the circuit capacitances (C in Fig. 6–7a) quickly and achieve a high circuit speed. An important factor that determines the MOSFET current is the electron or hole mobility in the surface inversion layer.

### 6.3.1 Surface Mobilities

Hu ch06v3.fm Page 201 Friday, February 13, 2009 4:51 PM

When a small  $V_{ds}$  is applied, the drain to source current,  $I_{ds}$ ,<sup>1</sup> in Fig. 6–6b is

$$I_{\rm ds} = W \cdot Q_{\rm inv} \cdot v = W Q_{\rm inv} \mu_{ns} \mathscr{E} = W Q_{\rm inv} \mu_{ns} V_{\rm ds} / L$$

$$= W C_{\rm oxe} (V_{\rm gs} - V_{\rm t}) \mu_{ns} V_{\rm ds} / L$$

(6.3.1)

W is the **channel width**, i.e., the channel dimension perpendicular to the page in Fig. 6–6 and the vertical dimension of the channel in Fig. 6–7c.  $Q_{inv}$  (C/cm<sup>2</sup>) is the inversion charge density [Eq. (5.5.3)]. **%** is the channel electric field, and L is the **channel length**.  $\mu_{ns}$  is the electron **surface mobility**, or the **effective mobility**. In MOSFETs,  $\mu_{ns}$  and  $\mu_{ps}$  (hole surface mobility) are several times smaller than the bulk mobilities presented in Section 2.2. In Eq. (6.3.1), all quantities besides  $\mu_{ns}$  are known in Eq. (6.3.1) or can be measured, and therefore  $\mu_{ns}$  can be determined.

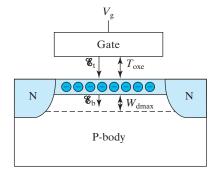

$\mu_{ns}$  is a function of the average of the electric fields at the bottom and the top of the inversion charge layer,  $\mathcal{E}_{b}$  and  $\mathcal{E}_{t}$  in Fig. 6–8 [4]. From Gauss's Law, using the depletion layer as the Gaussian box

$$\mathscr{E}_{\rm b} = -Q_{\rm dep}/\varepsilon_{\rm s} \tag{6.3.2}$$

From Eq. (5.4.4)

$$V_{\rm t} = V_{\rm fb} + \phi_{\rm st} - Q_{\rm dep} / C_{\rm oxe} \tag{6.3.3}$$

Therefore,

$$\mathscr{C}_{b} = \frac{C_{oxe}}{\varepsilon_{s}} (V_{t} - V_{fb} - \phi_{st})$$

(6.3.4)

**FIGURE 6–8** Surface mobility is a function of the average of the electric fields at the bottom and the top of the inversion charge layer,  $\mathscr{C}_b$  and  $\mathscr{C}_t$ .

<sup>&</sup>lt;sup>1</sup> We will follow the convention that positive  $I_{ds}$  refers to the normal direction of channel current from  $V_{dd}$  to ground, i.e., drain to source in NFET and source to drain in PFET. Therefore,  $I_{ds}$  is always positive.

Apply Gauss's Law to a box that encloses the depletion layer and the inversion layer.

$$\begin{aligned} \boldsymbol{\mathscr{E}}_{t} &= -(Q_{dep} + Q_{inv})/\varepsilon_{s} \\ &= \boldsymbol{\mathscr{E}}_{b} - Q_{inv}/\varepsilon_{s} = \boldsymbol{\mathscr{E}}_{b} + \frac{C_{oxe}}{\varepsilon_{s}}(V_{gs} - V_{t}) \\ &= \frac{C_{oxe}}{\varepsilon_{s}}(V_{gs} - V_{fb} - \phi_{st}) \end{aligned} \tag{6.3.5}$$

$$\frac{1}{2}(\boldsymbol{\mathscr{E}}_{b} + \boldsymbol{\mathscr{E}}_{t}) = \frac{C_{oxe}}{2\varepsilon_{s}}(V_{gs} + V_{t} - 2V_{fb} - 2\phi_{st}) \\ &\approx \frac{C_{oxe}}{2\varepsilon_{s}}(V_{gs} + V_{t} + 0.2 \text{ V}) \\ &= \frac{\varepsilon_{ox}}{2\varepsilon_{s}T_{oxe}}(V_{gs} + V_{t} + 0.2 \text{ V}) \\ &= \frac{V_{gs} + V_{t} + 0.2 \text{ V}}{6T_{oxe}} \quad \text{for N}^{+} \text{ poly-gate NFET} \tag{6.3.6} \end{aligned}$$

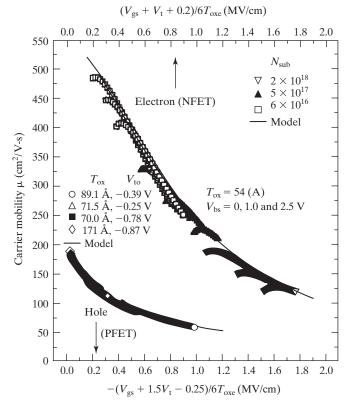

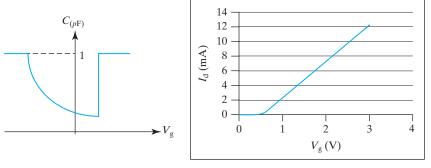

$\mu_{ns}$  has been found to be a function of the average of  $\mathscr{E}_{b}$  and  $\mathscr{E}_{t}$ . (This conclusion is sometimes presented with the equivalent statement that  $\mu_{ns}$  is a function of  $Q_{dep} + Q_{inv}/2$ .) The measured  $\mu_{ns}$  is plotted in Fig. 6–9 and can be fitted with [4]:<sup>2</sup>

$$\mu_{ns} = \frac{540 \,\mathrm{cm}^2 / \mathrm{Vs}}{1 + \left(\frac{V_{gs} + V_t + 0.2 \,\mathrm{V}}{5.4 \,T_{\mathrm{oxe}}}\right)^{1.85}} \tag{6.3.7}$$

Empirically, the hole surface mobility is a function of  $(\mathscr{E}_t + 1.5\mathscr{E}_b)/2$  [5].

$$\mu_{ps} = \frac{185 \,\mathrm{cm}^2 / \mathrm{Vs}}{1 - \left(\frac{V_{gs} + 1.5 \,\mathrm{V_t} - 0.25 \,\mathrm{V}}{3.38 \,T_{\mathrm{oxe}}}\right)} \tag{6.3.8}$$

$T_{\text{oxe}}$  is defined in Eq. (5.9.2). Normally,  $V_{\text{gs}}$  and  $V_{\text{t}}$  are negative for a PFET, i.e., in Eq. (6.3.8). This mobility model accounts for the effects of the major variables on the surface mobility. When device variables  $V_{\text{gs}}$ ,  $V_{\text{t}}$ , and  $T_{\text{oxe}}$  are properly considered, all silicon MOSFETs exhibit essentially the same surface mobility as illustrated in Fig 6–9. This is said to be Si's **universal effective mobility**. The surface mobility is lower than the bulk mobility because of **surface roughness scattering** [5, 6]. It makes the mobilities

<sup>&</sup>lt;sup>2</sup> Equation (6.3.7) is for the common case of NMOSFET with N<sup>+</sup> poly-Si gate. In general, the 0.2 V term should be replaced with  $-2(V_{\text{fb}} + \phi_{\text{st}})$ . See Eq. (5.4.2) for  $\phi_{\text{st}}$ . Eq. (6.3.8) is for the common case of PMOSFET with P<sup>+</sup> poly-Si gate. In general, the -0.25 V term should be replaced with  $2.5(V_{\text{fb}} + \phi_{\text{st}})$ .

Hu ch06v3.fm Page 203 Friday, February 13, 2009 4:51 PM

**FIGURE 6–9** Electron and hole surface mobilities are determined by  $V_{gs}$ ,  $V_t$ , and  $T_{oxe}$ .  $T_{oxe}$  is the SiO<sub>2</sub> equivalent electrical oxide thickness. (From [4]. © 1996 IEEE.)

### Effect of Wafer Surface Orientation and Drift Direction

The surface mobility is a function of the surface orientation and the drift direction. The standard CMOS technology employs the [100] surface silicon wafers, and the transistors are laid out so that the electrons and holes flow along the identical (0 ±1 ±1) directions on the wafer surface. (See Section 1.1 for explanation of the notation). One of the reasons for the choice is that this combination provides the highest  $\mu_{ns}$ , though not the highest  $\mu_{ps}$ . The mobility data in Fig. 6–9 are for this standard choice. The wafer orientation and current direction also determine how  $\mu_{ns}$  and  $\mu_{ps}$  respond to mechanical stress (see Section 7.1.2). These orientation effects can be explained by the solution of the Schrödinger's wave equation.

decrease as the field in the inversion layer ( $\mathcal{E}_b, \mathcal{E}_t$ ) becomes stronger and the charge carriers are confined closer to the Si–SiO<sub>2</sub> interface.  $\mu_{ns}$  and  $\mu_{ps}$  still roughly follow the  $T^{-3/2}$  temperature dependence that is

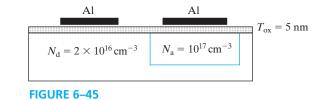

$\mu_{ns}$  and  $\mu_{ps}$  still roughly follow the  $T^{-3/2}$  temperature dependence that is characteristic of phonon scattering (see Eq. 2.2.5). In Fig. 6–9, the surface mobility around  $V_g \approx V_t$ , especially in the heavily doped semiconductor (2 × 10<sup>18</sup> cm<sup>-3</sup>), is lower than the universal mobility. Dopant ion scattering is the culprit. At higher  $V_g$ , dopant ion scattering effect is screened out by the inversion layer carriers (see Section 2.2.2).

#### **EXAMPLE 6–1**

What is the surface mobility at  $V_{gs} = 1$ V in an N-channel MOSFET with  $V_t = 0.3$  V and  $T_{oxe} = 2$  nm?

SOLUTION:

$(V_{gs} + V_t + 0.2)/6T_{oxe} = (1.5V/12 \times 10^{-7} \text{cm} = 1.25 \text{ MV/cm})$

A megavolt (10<sup>6</sup> V) is 1 MV. From Fig. 6–9,  $\mu_{ns} \approx 190 \text{ cm}^2/\text{V}\cdot\text{s}$ . To the dismay of MOSFET engineers, this is several times smaller than  $\mu_n$ , the bulk mobility.  $\mu_{ps}$  for a PMOSFET of similar design is only 60 cm<sup>2</sup>/V·s.

#### 6.3.2 GaAs MESFET

Higher carrier mobility allows the carriers to travel faster and the transistors to operate at higher speeds. High-speed devices not only improve the throughput of electronic equipment but also open up new applications such as inexpensive microwave communication. The most obvious way to improve speed is to use a semiconductor having higher mobility than silicon such as germanium, Ge (see Table 2–1) or strained Si (see Section 7.1.2). Single-crystalline Ge and SiGe alloy films can be grown epitaxially over Si substrates. The extension of Si technology to include Ge or SiGe transistor is a promising way to improve the device speed.

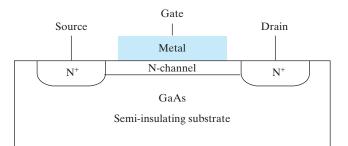

Table 2–1 indicates that GaAs and some other compound semiconductors have much higher electron mobilities than Si. For some applications, only N-channel FETs are needed and the hole mobility is of no importance. Unfortunately, it is very difficult to produce high-quality MOS transistors in these materials. There are too many charge traps at the semiconductor/dielectric interface for MOSFET application. Fortunately, a Schottky junction can serve as the control gate of a GaAs FET in place of an MOS gate. The device, called **MESFET** for **metal-semiconductor fieldeffect transistor**, is shown in Fig. 6–10. Because GaAs has a large  $E_g$  and small  $n_i$ , undoped GaAs has a very high resistivity and can be considered an insulator. The metal gate may be made of Au, for example. A large Schottky barrier height is desirable for minimizing the input gate current, i.e., the Schottky diode current.

When a reverse-bias voltage or a small forward voltage (small enough to keep the gate diode current acceptable) is applied to the gate, the depletion region under the gate expands or contracts. This modulates the thickness of the conductive channel, the part that is not depleted. This change, in turn, modulates the channel

FIGURE 6–10 Schematic of a Schottky gate FET called MESFET.

#### 6.3 • Surface Mobilities and High-Mobility FETs

current  $I_{ds}$ . Because  $I_{ds}$  does not flow in a surface inversion layer, the electron mobility is not degraded by surface scattering. This fact further enhances GaAs MESFET's speed advantage.

If the N-channel thickness is larger than the depletion-layer width at  $V_g = 0$ , the MESFET is conductive at  $V_g = 0$  and requires a (reverse bias) gate voltage to turn it off. It is called a **depletion-mode transistor**. If the N-channel is thinner than the depletion-layer width at  $V_g = 0$ , a (forward) gate voltage is needed to turn the transistor on. This is known as an **enhancement-mode transistor**. Modern Si MOSFETs are all enhancement-mode transistors, which make circuit design much easier. GaAs FETs of both depletion-mode and enhancement-mode types are used. The depletion-type device is easier to make.

### 6.3.3 HEMT

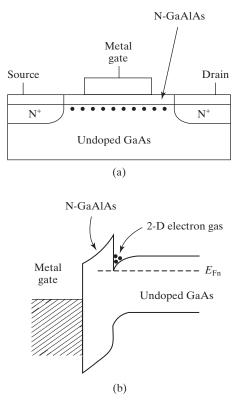

The dopants in the channel in Fig. 6–10 significantly reduce the electron mobility through impurity scattering (see Section 2.2.2). If the channel is undoped, the mobility can be much higher. A MOSFET does not rely on doping to provide the conduction channel. Can GaAs FET do the same? The answer is yes. A MOS-like structure can be made by growing a thin epitaxial layer of GaAlAs over the undoped GaAs substrate as shown in Fig. 6–11a. Under the gate the GaAlAs film is

**FIGURE 6–11** (a) The basic HEMT structure. The large band gap GaAlAs functions like the  $SiO_2$  in a MOSFET. The conduction channel is in the undoped GaAs. (b) The energy diagram confirms the similarity to a MOSFET.

depleted. GaAlAs has a larger band gap than GaAs and Fig. 6–11b shows that it functions like the oxide in a MOSFET (see Fig. 5–9) in that it creates an energy well and a thin layer of electrons at the GaAs–GaAlAs interface. The curvature in the GaAlAs band diagram is due to the presence of the dopant ions as in the depletion layer of a PN junction.  $E_F$  is the Fermi level of the N+ source and it (with  $E_c$ ) determines the electron concentration in the conduction channel. The channel electrons come from the N<sup>+</sup> source. Because the epitaxial interface of the two semiconductors is smoother than the Si–SiO<sub>2</sub> interface, this device does not suffer from mobility degradation by surface scattering as MOSFET does. This device is called **HEMT** or **high electron-mobility transistor**, or **MODFET** for **modulationdoped FET**. It is used in microwave communication, satellite TV receivers, etc.

#### 6.3.4 JFET

If the Schottky junction in Fig. 6–10 is replaced with a  $P^+N$  junction, the new structure is called a **JFET** or **junction field-effect transistor**. The  $P^+$  gate is of course connected to a metal for circuit connections. As in a MESFET, a reverse bias would expand the depletion layer and constrict the conduction channel. In this manner, the JFET current can be controlled with the gate voltage. Before the advent of MOSFET, ICs were built

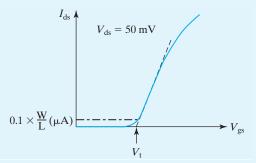

## How to Measure the V<sub>t</sub> of a MOSFET

$V_{\rm t}$  is rarely determined from the CV data. Instead it can be more easily measured from the  $I_{\rm ds} - V_{\rm gs}$  plot shown in Fig. 6–12.

**FIGURE 6–12**  $V_{\rm t}$  can be measured by extrapolating the  $I_{\rm ds}$  vs.  $V_{\rm gs}$  curve to  $I_{\rm ds} = 0$ . Alternatively, it can be defined as the  $V_{\rm gs}$ , at which  $I_{\rm ds}$  is a small fixed amount.

$I_{\rm ds}$  measured at a small  $V_{\rm ds}$  such as 50 mV is plotted against  $V_{\rm gs}$ . At  $V_{\rm gs} > V_t$ ,  $I_{\rm ds}$  increases linearly with  $(V_{\rm gs} - V_t)$  according to Eq. (6.3.1), if  $\mu_{ns}$  were a constant. Because  $\mu_{ns}$  decreases with increasing  $V_{\rm gs}$  (see Section 6.3), the curve is sublinear. It is a common practice to extrapolate the curve at the point of maximum slope and take the intercept with the x-axis as  $V_t$ .

An increasingly popular alternative is to define  $V_t$  as the  $V_{gs}$  at which  $I_{ds}$  is equal to a small value such as

$$I_{\rm ds} = 0.1 \ \mu \rm A \times \frac{W}{L}$$

Also see Fig. 7-2 d.

207

with bipolar transistors, which have forward-biased diodes at the input and draw significant input current (see Chapter 8). The high input currents and capacitances were quite undesirable for some circuits. JFET provided a low input current and capacitance device because its input is a reverse-biased diode. JFET can be fabricated with bipolar transistors and coexist in the same IC chip.

### 6.4 • MOSFET V<sub>t</sub>, BODY EFFECT, AND STEEP RETROGRADE DOPING •

Hu\_ch06v3.fm Page 207 Friday, February 13, 2009 4:51 PM

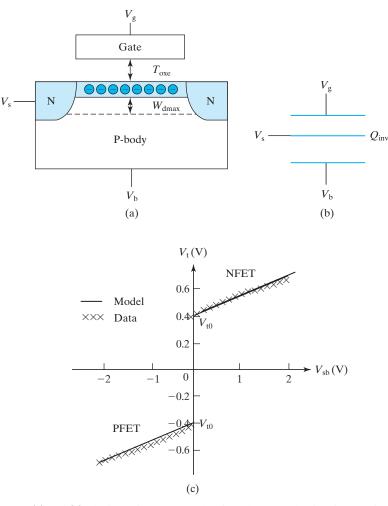

The inversion layer of a MOSFET can be thought of as a resistive N-type film (1-2 nm thin) that connects the source and the drain as shown in Fig. 6–13. This film, at potential  $V_s$ , forms a capacitor with the gate, the oxide being the capacitor

**FIGURE 6–13** (a) and (b) The inversion layer can be viewed as a conductive film that is coupled to  $V_g$  through the oxide capacitance and coupled to  $V_b$  through the depletion-layer capacitance. The drain is open-circuited. (c)  $V_t$  is an approximately linear function of the body to source bias voltage. The polarity of the body bias is normally that which would reverse bias the body-source junction.

208

#### Chapter 6 MOS Transistor

dielectric. It also forms a second capacitor with the body and the capacitor dielectric is the depletion layer. The depletion-layer capacitance is

$$C_{\rm dep} = \frac{\varepsilon_{\rm s}}{W_{\rm dmax}} \tag{6.4.1}$$

In Chapter 5, with  $V_b = V_s$ , we concluded that the gate voltage induces a charge in the invesion layer,

$$Q_{\rm inv} = -C_{\rm oxe}(V_{\rm gs} - V_{\rm t})$$

(6.4.2)

Let us now assume that there is also a voltage between the source and the body,  $V_{\rm sb}$ . Since the body and the channel are coupled by  $C_{\rm dep}$ ,  $V_{\rm sb}$  induces a charge in the inversion layer,  $C_{\rm dep}V_{\rm sb}$ . Therefore

$$Q_{\rm inv} = -C_{\rm oxe}(V_{\rm gs} - V_{\rm t}) + C_{\rm dep}V_{\rm sb}$$

(6.4.3)

$$= -C_{\text{oxe}} \left( V_{\text{gs}} - \left( V_{\text{t}} + \frac{C_{\text{dep}}}{C_{\text{oxe}}} V_{\text{sb}} \right) \right)$$

(6.4.4)

Equation (6.4.4) can be rewritten in the simple form of Eq. (6.4.2) if we adopt a modification to  $V_t$ . (What we have called  $V_t$  up to this point will henceforth be called  $V_{t0}$ .)

$$Q_{\rm inv} = -C_{\rm oxe}(V_{\rm gs} - V_{\rm t}(V_{\rm sb}))$$

(6.4.5)

$$V_{\rm t}(V_{\rm sb}) = V_{\rm t0} + \frac{C_{\rm dep}}{C_{\rm oxe}} V_{\rm sb} = V_{\rm t0} + \alpha V_{\rm sb}$$

(6.4.6)

$$\alpha = C_{\rm dep} / C_{\rm oxe} = 3T_{\rm oxe} / W_{\rm dmax}$$

(6.4.7)

The factor 3 is the ratio of the relative dielectric constants of silicon (11.9) and SiO<sub>2</sub> (3.9). Figure 6–13c illustrates the conclusion that  $V_t$  is a function of  $V_{sb}$ . When the source-body junction is reverse-biased, the NFET  $V_t$  becomes more positive and the PFET  $V_t$  becomes more negative. Normally, the source-body junctions are never forward biased so that there is no forward diode current.

The fact that  $V_t$  is a function of the body bias is called the **body effect**. When multiple NFETs (or PFETs) are connected in series in a circuit, they share a common body (the silicon substrate) but their sources do not have the same voltage. Clearly some transistors' source-body junctions are reversed biased. This raises their  $V_t$  and reduces  $I_{ds}$  and the circuit speed. Circuits therefore perform best when  $V_t$  is as insensitive to  $V_{sb}$  as possible, i.e., the body effect should be minimized. This can be accomplished by minimizing the  $T_{ox}/W_{dmax}$  ratio. (We will see again and again that a thin oxide is desirable.)  $\alpha$  in Eq. (6.4.6) can be extracted from the slope of the curve in Fig. 6–13c and is called the **body-effect coefficient**.

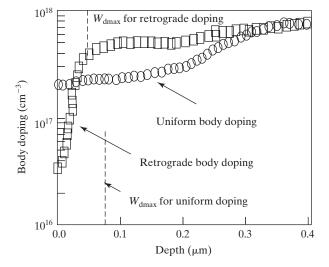

Modern transistors employ steep **retrograde body doping profiles** (light doping in a thin surface layer and very heavy doping underneath) illustrated in Fig. 6–14. Steep retrograde doping allows transistor shrinking to smaller sizes for cost reduction and reduces impurity scattering. Section 7.5 explains why. The depletion-layer thickness is basically the thickness of the lightly doped region. As  $V_{\rm sb}$  increases, the depletion layer does not change significantly. Therefore  $C_{\rm dep}$  and

FIGURE 6–14 Comparison of a steep retrograde doping profile and a uniform doping profile.

$\alpha$  are basically constants. As a result, modern transistors exhibit a more or less linear relationship between  $V_{\rm t}$  and  $V_{\rm sb}$ . A linear relationship means that  $W_{\rm dmax}$  and therefore the  $C_{\rm dep}/C_{\rm oxe}$  ratio are independent of the body bias.

In earlier generations of MOSFETs, the body doping density is more or less uniform (see the lower curve in Fig. 6–14) and  $W_{dmax}$  varies with  $V_{sb}$ . In that case, the theory for the body effect is more complicated.  $V_t$  can be obtained by replacing the  $2\phi_B$  term (band bending in the body) in Eq. (5.4.3) with  $2\phi_B + V_{sb}$ .<sup>3</sup>

$$V_{t} = V_{t0} + \frac{\sqrt{qN_{a}2\varepsilon_{s}}}{C_{oxe}} (\sqrt{2\phi_{B} + V_{sb}} - \sqrt{2\phi_{B}})$$

$$\equiv V_{t0} + \gamma (\sqrt{2\phi_{B} + V_{sb}} - \sqrt{2\phi_{B}})$$

(6.4.8)

$\gamma$  is called the **body-effect parameter**. Equation (6.4.8) predicts that  $V_t$  is a sublinear function of  $V_{sb}$ . A hint of the sublinearity is observable in the data in Fig. 6–13c. Equation (6.4.8) is sometimes linearized by Taylor expansion so that  $V_t$  is expressed as a linear function of  $V_{sb}$  in the form of Eq. (6.4.6).

### 6.5 • QINV IN MOSFET •

Let us consider Fig. 6–15 with  $V_d > V_s$ . The channel voltage,  $V_c$ , is now a function of x.  $V_c = V_s$  at x = 0 and  $V_c = V_d$  at x = L. Compare a point in the middle of the channel where  $V_c > V_s$  with a point at the source-end of the channel, where

<sup>&</sup>lt;sup>3</sup> When the source-body junction is reverse biased, there are two quasi-Fermi levels,  $E_{\text{Fn}}$  and  $E_{\text{Fp}}$  (similar to Fig. 4–7c with the P-region being the MOSFET body and the N-region being the source), which are separated by  $qV_{\text{sb}}$ . The inversion layer does not appear when  $E_c$  at the interface is close to  $E_{\text{Fp}}$  ( $E_{\text{F}}$  in Fig. 5–7). It appears when  $E_{\text{F}}$  is close to  $E_{\text{Fn}}$  ( $qV_{\text{sb}}$  below  $E_{\text{F}}$  in Fig. 5–7). This requires the band bending to be  $2\phi_{\text{B}} + V_{\text{sb}}$  not  $2\phi_{\text{B}}$ .

**FIGURE 6–15** When  $V_{ds} \neq 0$ , the channel voltage  $V_c$  is a function of x.

$V_{\rm c} = V_{\rm s}$ . Because the voltage in the middle of the channel is higher at  $V_{\rm c}(x)$ , there is less voltage across the oxide capacitor (and across the depletion layer capacitor). Therefore, there will be fewer electrons on the capacitor electrode (the inversion layer). Specifically, the  $V_{\rm gs}$  term in Eq. (6.4.5) should be replaced by  $V_{gc}(x)$  or  $V_{gs} - V_{cs}(x)$  and  $V_{sb}$  by  $V_{sb} + V_{cs}(x)$ .

$$Q_{inv}(x) = -C_{oxe}(V_{gs} - V_{cs} - V_{t0} - \alpha(V_{sb} + V_{cs}))$$

=  $-C_{oxe}(V_{gs} - V_{cs} - (V_{t0} + \alpha V_{sb}) - \alpha V_{cs})$

=  $-C_{oxe}(V_{gs} - mV_{cs} - V_{t})$  (6.5.1)

$$m \equiv 1 + \alpha = 1 + C_{dep}/C_{oxe} = 1 + 3T_{oxe}/W_{dmax}$$

(6.5.2)

*m* is typically around 1.2. It is acceptable and easier at the beginning to simply assume m = 1. However, including m in the equations significantly improves their accuracies for later reference. The body is sometimes called the **back gate** since it clearly has a similar though weaker effect on the channel charge. The back-gate effect on  $Q_{inv}$  is often called the **bulk-charge effect**. *m* is called the **bulk-charge** factor. Clearly the bulk-charge effect is closely linked to the body-effect of Section 6.4.

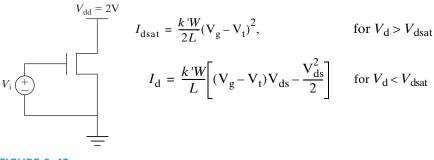

#### 6.6 **BASIC MOSFET IV MODEL** •

Using Eq. (6.5.1) and dropping the negative sign for simplicity ( $I_{ds}$  in Fig. 6–15 is understood to flow from the high-voltage terminal to the low-voltage terminal).

$$I_{\rm ds} = W \cdot Q_{\rm inv}(x) \cdot v = W \cdot Q_{\rm inv} \mu_{ns} \mathscr{C}$$

=  $W C_{\rm oxe} (V_{\rm gs} - mV_{\rm cs} - V_{\rm t}) \mu_{ns} dV_{\rm cs} / dx$  (6.6.1)

#### 6.6 • Basic MOSFET IV Model

$$\int_{0}^{L} I_{\rm ds} dx = W C_{\rm oxe} \mu_{ns} \int_{0}^{V_{\rm ds}} (V_{\rm gs} - mV_{\rm cs} - V_{\rm t}) dV_{\rm cs}$$

(6.6.2)

$$I_{\rm ds}L = WC_{\rm oxe}\mu_{ns} \left(V_{\rm gs} - V_{\rm t} - \frac{m}{2}V_{\rm ds}\right)V_{\rm ds}$$

(6.6.3)

$$I_{\rm ds} = \frac{W}{L} C_{\rm oxe} \mu_{ns} \left( V_{\rm gs} - V_{\rm t} - \frac{m}{2} V_{\rm ds} \right) V_{\rm ds}$$

(6.6.4)

Equation (6.6.4) shows that  $I_{ds}$  is proportional to W (channel width),  $\mu_{ns}$ ,  $V_{ds}/L$  (the average field in the channel), and  $C_{ox}(V_g - V_t - mV_{ds}/2)$ , which may be interpreted as the average  $Q_{inv}$  in the channel. When  $V_{ds}$  is very small, the  $mV_{ds}/2$  term is negligible and  $I_{ds} \propto V_{ds}$ , i.e., the transistor behaves as a resistor. As  $V_{ds}$  increases, the average  $Q_{inv}$  decreases and  $dI_{ds}/dV_{ds}$  decreases. By differentiating Eq. (6.6.4) with respect to  $V_{ds}$ , it can be shown that  $dI_{ds}/dV_{ds}$  becomes zero at a certain  $V_{ds}$ .

$$\frac{dI_{ds}}{dV_{ds}} = 0 = \frac{W}{L}C_{ox}\mu_{ns}(V_{gs} - V_t - mV_{ds}) \quad \text{at} \quad V_{ds} = V_{dsat}$$

$$V_{dsat} = \frac{V_{gs} - V_t}{m} \quad (6.6.5)$$

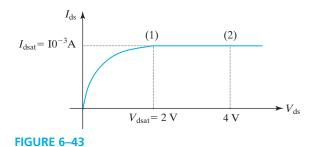

$V_{\rm dsat}$  is called the **drain saturation voltage**, beyond which the drain current is saturated as shown in Fig. 6–16. For each  $V_{\rm g}$ , there is a different  $V_{\rm dsat}$ . The part of the *IV* curves with  $V_{\rm ds} \ll V_{\rm dsat}$  is the **linear region**, and the part with  $V_{\rm ds} > V_{\rm dsat}$  is the **saturation region**. Analog designers often refer to the regions as the **Ohmic region** and the **active region**.

FIGURE 6–16 MOSFET IV characteristics.

The saturation current can be obtained by substituting  $V_{\text{dsat}}$  [Eq. (6.6.5)] for  $V_{\text{ds}}$  in Eq. (6.6.4).

$$I_{\rm dsat} = \frac{W}{2 \,{\rm mL}} C_{\rm oxe} \mu_{ns} (V_{\rm gs} - V_{\rm t})^2$$

(6.6.6)

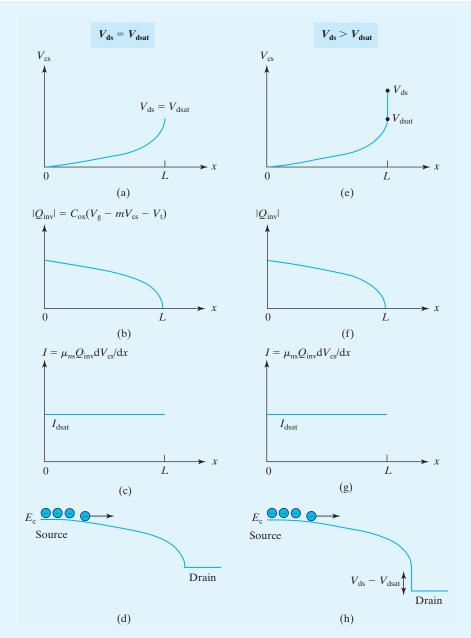

What happens at  $V_d = V_{dsat}$  and why does  $I_{ds}$  stay constant beyond  $V_{dsat}$ ? The first question can be answered by substituting  $V_{dsat}$  [Eq. (6.6.5)] for  $V_{cs}$  in Eq. (6.5.1).  $Q_{inv}$  at the drain end of the channel, when  $V_{ds} = V_{dsat}$ , is zero! This disappearance of the inversion layer is called channel **pinch-off**. Figure 6–17 plots  $V_{cs}$ ,  $Q_{inv}$ , and  $I_{ds}$  at  $V_{ds} = V_{dsat}$  and  $V_{ds} > V_{dsat}$ . In these two cases,  $V_{cs}(x)$ ,  $Q_{inv}(x)$  and therefore  $I_{ds}$  are the same. This explains why  $I_{ds}$  does not change with  $V_{ds}$  beyond  $V_{dsat}$ . The only difference is that, at  $V_{ds} > V_{dsat}$ , there exists a short, high-field **pinch-off region** where  $Q_{inv} = 0$  and across which the voltage  $V_{ds} - V_{dsat}$  is dropped. Section 6.9.1 will present an improvement to the concept of pinch-off such that  $Q_{inv}$  does not drop to zero. For now, the concept of pinch-off is useful for introducing the phenomenon of current saturation.

How can a current flow through the pinch-off region, which is similar to a depletion region? The fact is that a depletion region does not stop current flow as long as there is a supply of the right carriers. For example, in solar cells and photodiodes, current can flow through the depletion region of PN junctions. Similarly, when the electrons reach the pinch-off region of a MOSFET, they are swept down the steep potential drop in Fig. 6–17h. Therefore, the pinch-off region does not present a barrier to current flow. Furthermore, Fig. 6–17d and h show that the electron flow rates (current) are equal in the two cases because they have the same drift field and  $Q_{inv}$  in the channel. In other words, the current is independent of  $V_{ds}$  beyond  $V_{dsat}$ . The situation is like a mountain stream feeding into a waterfall. The slope of the river bed  $(dE_c/dx)$  and the amount of water in the stream determine the water flow rate in the stream, which in turn determines the flow rate down the waterfall. The height of the waterfall ( $V_{ds} - V_{dsat}$ ), whether 1 or 100 m, has no influence over the flow rate.

#### Channel Voltage Profile

First consider the case of  $V_{ds} = V_{dsat}$ . Substituting the upper limits of integration in Eq. (6.6.2), L and  $V_{ds}$ , with x and  $V_{cs}$  and using  $I_{ds} = I_{dsat} = Eq.$  (6.6.6), you can show that (see Problem 6.9 at the end of the chapter).

$$V_{\rm cs} = \frac{V_{\rm gs} - V_{\rm t}}{m} \left( 1 - \sqrt{1 - \frac{x}{L}} \right)$$

(6.6.7)

As expected,  $V_{cs} = 0$  at x = 0 and  $V_{cs} = V_{dsat} = (V_g - V_t)/m$  at x = L. From this, you can show that  $WQ_{inv}\mu_s \mathscr{E}$  or  $WC_{ox}(V_{gs} - mV_{cs} - V_t)\mu_s dV_{cs}/dx$  is independent of x and yields the  $I_{dsat}$  expressed in Eq. (6.6.6). Equation (6.6.7) is plotted in Fig. 6–17a.

See Fig. 6–17e for the  $V_{ds} > V_{dsat}$  case.  $V_{cs}$  still follows Eq. (6.6.7) from the source to the beginning of the pinch-off region.  $V_{ds} - V_{dsat}$  is dropped in a narrow pinch-off region next to the drain.

•

Transconductance, defined as

$$g_{\rm m} \equiv \left. dI_{\rm ds} / \left. dV_{\rm gs} \right|_{V_{\rm ds}} \tag{6.6.8}$$

is a measure of a transistor's sensitivity to the input voltage. In general, a large  $g_m$  is desirable. Substituting Eq. (6.6.6) into Eq. (6.6.8), we find

$$g_{\rm msat} = \frac{W}{mL} C_{\rm oxe} \mu_{ns} (V_{\rm gs} - V_{\rm t})$$

(6.6.9)

### 6.7 • CMOS INVERTER—A CIRCUIT EXAMPLE •

Transistors' influences on circuits will be illustrated using CMOS inverters, which were introduced in Section 6.2. They consume little power and have the important property of regenerating or cleaning up the digital signal. The latter property will be discussed in detail in Section 6.7.1. The speed of the inverters is analyzed in Section 6.7.2.

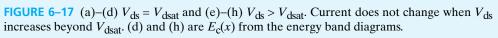

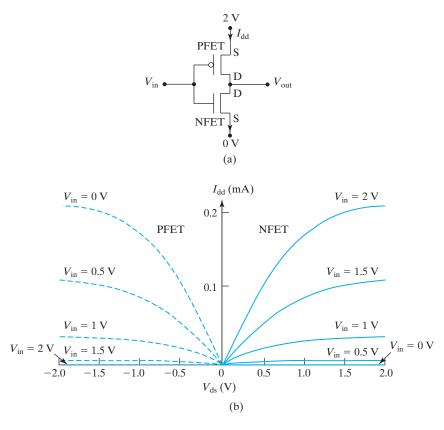

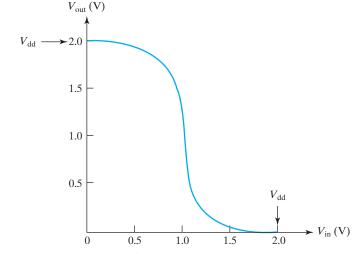

### 6.7.1 Voltage Transfer Curve (VTC)

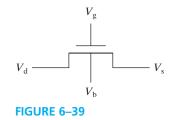

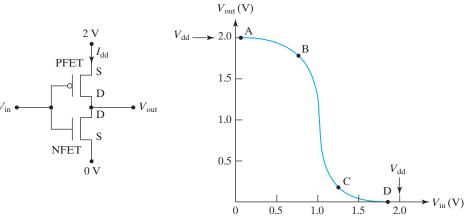

Consider the CMOS inverter shown in Fig. 6–18a. The NFET IV characteristics are similar to those shown in Fig. 6–16 and are plotted on the right half of Fig. 6–18b. Assume that the PFET has identical (symmetric) IV as plotted on the left half of the figure. From (a), the  $V_{\rm ds}$  of the PFET and NFET are related to  $V_{\rm out}$  by  $V_{\rm dsN} = V_{\rm out}$  and  $V_{\rm dsP} = V_{\rm out} - 2$  V. Therefore, the two halves of (b) can be replotted in (c) using  $V_{\rm out}$  as the common variable. For example, at  $V_{\rm out} = 2$ V in (c),  $V_{\rm dsN} = 2$ V and  $V_{\rm dsP} = 0$  V.

The two  $V_{in} = 0$  curves in (c) intersect at  $V_{out} = 2$  V. This means  $V_{out} = 2$  V when  $V_{in} = 0$  V. This point is recorded in Fig. 6–19. The two  $V_{in} = 0.5$  V curves intersect at around  $V_{out} = 1.9$  V. The two  $V_{in} = 1$  V curves intersect at  $V_{out} = 1$  V. All the  $V_{in}/V_{out}$  pairs are represented by the curve in Fig. 6–19, which is the **voltage transfer characteristic** or **voltage transfer curve** or **VTC** of the inverter. The VTC provides the important noise margin of the digital circuits.  $V_{in}$  may be anywhere between 0 V and the NFET  $V_t$  and still produce a perfect  $V_{out} = V_{dd}$ . Similarly,  $V_{in}$  may be anywhere between 2V and 2 V plus the PFET  $V_t$  and produce a perfect  $V_{out} = 0$  V. Therefore, perfect "0" and "1" outputs can be produced by somewhat corrupted inputs. This regenerative property allows complex logic circuits to function properly in the face of inductive and steep middle region would maximize the noise tolerance. Device characteristics that contribute to a desirable VTC include a large  $g_{m}$ , low leakage in the off state, and a small  $\partial I_{ds}/\partial V_{ds}$  in the saturation region. The latter two device properties will be discussed further in the next chapter.

For optimal circuit operation, the sharp transition region of the VTC should be located at or near  $V_{in} = V_{dd}/2$ . To achieve this symmetry, the *IV* curves of NFET and PFET Fig. 6–18b need to be closely matched (symmetric). This is accomplished by choosing a larger *W* for the PFET than the NFET. The  $W_P/W_N$  ratio is usually around two to compensate for the fact that  $\mu_{ps}$  is smaller than  $\mu_{ns}$ . Hu\_ch06v3.fm Page 215 Friday, February 13, 2009 4:51 PM

♦

۲

**FIGURE 6–18** (a) CMOS inverter; (b) IV characteristics of NFET and PFET; and (c)  $V_{\text{out}} = V_{\text{dsN}} = 2 \text{ V} + V_{\text{dsP}}$  according to (a).

FIGURE 6–19 The VTC of a CMOS inverter.

# 6.7.2 Inverter Speed—The Importance of Ion

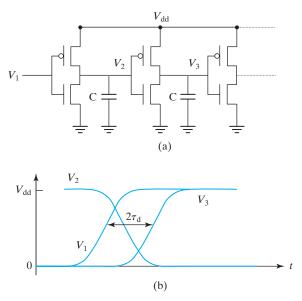

Propagation delay is the time delay for a signal to propagate from one gate to the next in a chain of identical gates as shown in Fig. 6–20.

$\tau_{\rm d}$  is the average of the delays of pull-down (rising  $V_1$  pulling down the output,  $V_2$ ) and pull-up (falling  $V_2$  pulling up the output,  $V_3$ ). The propagation delay of an inverter may be expressed as [7]

$$\tau_{\rm d} \approx \frac{CV_{\rm dd}}{4} \left( \frac{1}{I_{\rm onN}} + \frac{1}{I_{\rm onP}} \right) \tag{6.7.1}$$

**FIGURE 6–20** (a) A CMOS inverter chain. A circle on the gate indicates a PFET. (b) Propagation delay,  $\tau_d$ , defined.

where  $I_{onN}$  is taken at  $V_{gs} = V_{dd}$  and  $I_{onP}$  taken at  $V_{gs} = -V_{dd}$ . They are called the **on-state current**, of the NFET and the PFET

$$I_{\rm on} \equiv I_{\rm dsat} \Big|_{\rm maximum} |V_{\rm gs}| \tag{6.7.2}$$

Equation (6.7.1) has a simple explanation

$$\tau_{\rm d} = \frac{1}{2}$$

(pull-down delay + pull-up delay) (6.7.3)

pull-down delay

$$\approx \frac{CV_{\rm dd}}{2I_{\rm onN}}$$

pull-up delay  $\approx \frac{CV_{\rm dd}}{2I_{\rm onP}}$  (6.7.4)

The delay is the time for the on-state transistor supplying a current,  $I_{on}$ , to change the output by  $V_{dd}/2$  (not  $V_{dd}$ ).  $V_{dd}/2$  is plausible in view of Fig. 6–17. The charge drained from (or supplied to) C by the FET during the delay is  $CV_{dd}/2$ . Therefore, the delay is  $Q/I = CV_{dd}/2I_{on}$ . One may interpret the delay as RC with  $V_{dd}/2I_{on}$  as the switching resistance of the transistor. In order to maximize circuit speed it is clearly important to maximize  $I_{on}$ . We will further improve the  $I_{on}$  model in the next two sections.

The capacitance C represents the sum of all the capacitances that are connected to the output node of the inverter. They are the input capacitance of the next inverter in the chain, all the parasitic capacitances of the drain, and the capacitance of the metal interconnect that feeds the output voltage to the next inverter. In a large circuit, some interconnect metal lines can be quite long and their capacitances slow down the circuit significantly. This is ameliorated with the low-k dielectric technology described in Section 3.8 and circuit design techniques such as using a transistor with large W (a large  $I_{on}$ ) to drive a longer interconnect and using repeaters.

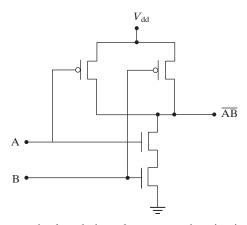

Although the inverter is a very simple circuit, it is the basis of other more complex logic gates and memory cells. For example, Fig. 6–21 shows a NAND gate with two inputs. It is an inverter circuit with two series transistors in the pull-down path and two parallel transistors in the pull-up path.

FIGURE 6–21 Inverters are the foundation of more complex circuits such as this two-input NAND gate.

#### Ring Oscillators •

$\tau_{\rm d}$  of a logic gate can be conveniently measured by connecting the end of a chain of identical logic gates (see Fig. 6–20a, for example) to the beginning of the chain to form a **ring oscillator**. The signal of any of the drain nodes in the ring oscillates with a period equal to  $\tau_{\rm d}$  times the number of gates in the ring. By using a large number of gates in the ring, the oscillation frequency can be conveniently low for easy measurement. Dividing the measured period of oscillation by the number of gates yields  $\tau_{\rm d}$ .

The number of gates in a ring oscillator must be an odd number such as 91. If the number is an even number such as 92, the circuit will not oscillate. Instead, it will be static at one of two stable states.

#### 6.7.3 Power Consumption

An important goal of device design is to minimize circuit power consumption. In each switching cycle, a charge  $CV_{dd}$  is transferred from the power supply to the load, *C*. The charge taken from the power supply in each second,  $kCV_{dd}f$ , is the average current provided by the power supply. Here, *f* is the clock frequency and k(<1) is an **activity factor** that represents the fact that a particular gate in a given circuit is not switched every clock cycle all the time. Therefore

$$P_{\text{dynamic}} = V_{\text{dd}} \times \text{average current} = k C V_{\text{dd}}^2 f$$

(6.7.6)

This **dynamic power** dominates the power consumption when the inverter is switched frequently. *Power consumption can be reduced by lowering*  $V_{dd}$  *and by minimizing all capacitances in the circuit as well as by reducing k*. It is interesting to note that making  $I_{on}$  large by using a small L or improving the carrier mobility does not increase  $P_{dynamic}$ .

It is desirable for a transistor to provide a large  $I_{on}$  (to reduce circuit switching delay) at a low  $V_{dd}$  (to reduce circuit power consumption). Reducing the transistor L and W, other parameters being equal, would lower C through reduction in the gate capacitance and the source-drain junction capacitance. Furthermore, smaller transistors make the chip smaller and therefore reduce the interconnect capacitance, too. Both device size reduction and  $V_{dd}$  reduction have been powerful means of lowering the power consumption per circuit function.

Another component of power consumption is the **static power**, or **leakage power** or **stand-by power** that is consumed when the inverter is static.

$$P_{\text{static}} = V_{\text{dd}} I_{\text{off}} \tag{6.7.7}$$

$I_{\rm off}$  is the off-state leakage current when the transistor is supposed to be off. In an ideal transistor,  $I_{\rm off}$  would be zero. It is difficult to keep  $I_{\rm off}$  low in very high speed IC technologies as explained in detail in Chapter 7. The total power consumption is

$$P_{\text{static}} = P_{\text{static}} + P_{\text{dynamic}} \tag{6.7.8}$$

#### 6.8 • Velocity Saturation

6.8 • VELOCITY SATURATION •

A major weakness of the basic MOSFET IV model is that a finite current flows through the pinch-off region, where  $Q_{inv} = 0$ . This requires the carrier velocity to be infinite, a physical impossibility. We will now remove this shortcoming.

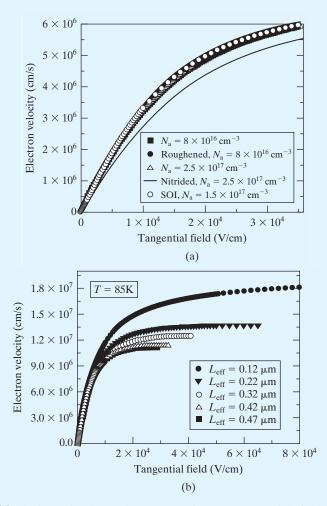

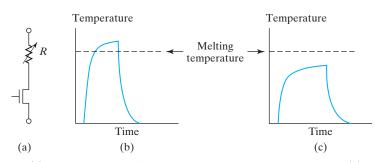

When the electric field is low, the carrier drift velocity, v, is  $\mu$ <sup>2</sup>. As <sup>2</sup> increases, the kinetic energy of the carriers rises. When the energy of a carrier exceeds the optical phonon energy,<sup>4</sup> it generates an optical phonon and loses much of its velocity. Consequently, the kinetic energy and therefore the drift velocity cannot exceed a certain value. The limiting velocity is called the **saturation velocity**. The *v*–<sup>2</sup> relationship is shown in Fig. 6–22.

The flattening of the v- $\mathscr{C}$  curve is called **velocity saturation** and can be approximated with

$$\mathbf{v} = \frac{\mu_{ns} \boldsymbol{\mathscr{E}}}{1 + \boldsymbol{\mathscr{E}} / \boldsymbol{\mathscr{E}}_{sat}} \tag{6.8.1}$$

where  $\mu_{ns}$  is the electron surface mobility and  $\mathscr{E}_{sat}$  is the field at which velocity saturation becomes significant or dominant. When  $\mathscr{E} << \mathscr{E}_{sat}$ , Eq. (6.8.1) reduces to  $v = \mu \mathscr{E}$ . When  $\mathscr{E} >> \mathscr{E}_{sat}$ , v is a constant regardless of how large  $\mathscr{E}$  is. Velocity saturation has a large and deleterious effect on the  $I_{on}$  of MOSFETs.

#### Velocity Overshoot

Figure 6–22b shows the v– $\mathscr{C}$  characteristics of inversion-layer electrons at 85 K [8]. This is offered as clearer evidence that velocity saturates at high field than the room-temperature data (Fig. 6–22a). Because the velocity saturation phenomenon is clearer, we can see an important detail— $v_{sat}$  is larger in transistors with very small channel lengths.

In the basic velocity-saturation model,  $v_{sat}$  is independent of the channel length. However, this figure shows that  $v_{sat}$  becomes larger when L is very small. When the channel length is sufficiently small, electrons may pass through the channel in too short a time for all the energetic carriers to lose energy by emitting optical phonons. As a result, the carriers can attain somewhat higher velocities in very small devices. This phenomenon is called **velocity overshoot**.

Velocity overshoot frees the extremely short transistors from the limit of velocity saturation. Unfortunately, another velocity limit (see Section 6.12) sets in before velocity overshoot offers a lot of relief.

<sup>&</sup>lt;sup>4</sup> Optical phonon is a type of phonons (atom vibration) that has much higher energy than the acoustic phonons that are partially responsible for the low-field mobility (see Section 2.2.2). The optical phonons involve large displacements of neighboring atoms. These displacements create electrical dipole field that interact very strongly with electrons and holes. An electron or a hole that has enough energy to generate an optical phonon will do so readily and lose its kinetic energy in the process.

**FIGURE 6–22** (a) The inversion-layer electron velocity saturates at high field regardless of the body doping concentration and surface treatment. (b) Velocity saturation is more prominent at low temperature. Velocity overshoot is also evident. (From [8]). © 1997 IEEE.)

### 6.9 MOSFET IV MODEL WITH VELOCITY SATURATION

The basic MOSFET IV theory presented in Section 6.6 assumes a constant mobility. It provides an excellent introduction to the theory of MOSFET. The present section refines the theory by including the important velocity saturation effect. If we apply Eq. (6.8.1) to Eq. (6.6.1), using an NMOSFET for example

$$I_{\rm ds} = WC_{\rm oxe}(V_{\rm gs} - mV_{\rm cs} - V_{\rm t}) \frac{\mu_{ns} dV_{\rm cs}/dx}{1 + \frac{dV_{\rm cs}}{dx}/\mathscr{E}_{\rm sat}}$$

(6.9.1)

#### 6.9 • MOSFET IV Model with Velocity Saturation

$$\int_{0}^{L} I_{\rm ds} dx = \int_{0}^{V_{\rm ds}} [WC_{\rm oxe} \mu_{ns} (V_{\rm gs} - mV_{\rm cs} - V_{\rm t}) - I_{\rm ds} / \mathscr{E}_{\rm sat}] dV_{\rm cs}$$

(6.9.2)

$$I_{\rm ds} = \frac{\frac{W}{L}C_{\rm oxe}\mu_{ns}\left(V_{\rm gs} - V_{\rm t} - \frac{m}{2}V_{\rm ds}\right)V_{\rm ds}}{1 + \frac{V_{\rm ds}}{\mathscr{C}_{\rm sat}L}}$$

(6.9.3)

When L is large, Eq. (6.9.3) reduces to Eq. (6.6.4). Therefore the latter is known as the **long-channel IV model**.

$$I_{\rm ds} = \frac{\text{long-channel } I_{\rm ds} (\text{Eq.} (6.6.4))}{1 + V_{\rm ds} / \mathscr{C}_{\rm sat} L}$$

(6.9.4)

The effect of velocity saturation is to reduce  $I_{ds}$  by a factor of  $1 + V_{ds}/\mathscr{E}_{sat}L$ . This factor reduces to one (i.e., velocity saturation becomes negligible) when  $V_{ds}$  is small or L is large. This factor may be interpreted as  $1 + \mathscr{E}_{ave}/\mathscr{E}_{sat}$ , where  $\mathscr{E}_{ave} \equiv V_{ds}/L$  is the average channel field. The saturation voltage,  $V_{dsat}$ , can be found by solving  $dI_{ds}/dV_{ds} = 0$ :

$$V_{\rm dsat} = \frac{2(V_{\rm gs} - V_{\rm t})/m}{1 + \sqrt{1 + 2(V_{\rm gs} - V_{\rm t})/m\mathcal{E}_{\rm sat}L}}$$

(6.9.5)

Equation (6.9.5) is rather inconvenient to use. A simpler and even more accurate  $V_{\text{dsat}}$  model may be derived from a piece-wise model that actually fits the  $v-\mathscr{C}$  data better than Eq. (6.8.1)[9]. It assumes that

$$v = \frac{\mu_{ns} \mathscr{E}}{1 + \mathscr{E} / \mathscr{E}_{sat}} \qquad \text{for } \mathscr{E} \le \mathscr{E}_{sat} \tag{6.9.6}$$

$$v = v_{sat} \qquad \text{for } \mathscr{C} \geq \mathscr{C}_{sat} \qquad (6.9.7)$$

Equating Eqs. (6.9.6) and (6.9.7) at  $\mathscr{C} = \mathscr{C}_{sat}$  yields

$$\mathscr{C}_{\text{sat}} = 2v_{\text{sat}}/\mu_{ns} \tag{6.9.8}$$

Equation (6.9.6) leads to Eq. (6.9.3), which is valid when the carrier speed is less than  $v_{sat}$ , i.e.,  $V_{ds} \le V_{dsat}$ . Equation (6.9.7) leads to the following equation describing the current at the drain end of the channel at the onset of velocity saturation (i.e., at  $V_d = V_{dsat}$ ):

$$I_{ds} = WQ_{inv}v$$

=  $WC_{oxe}(V_g - V_t - mV_{dsat})v_{sat}$  (6.9.9)

Equating Eqs. (6.9.3) and (6.9.9) leads to

$$\frac{1}{V_{\rm dsat}} = \frac{m}{V_{\rm gs} - V_{\rm t}} + \frac{1}{\mathscr{E}_{\rm sat}L}$$

(6.9.10)

$V_{\text{dsat}}$  in Eq. (6.9.6) is an average of  $\mathscr{C}_{\text{sat}}L$  and the long-channel  $V_{\text{dsat}}$ ,  $(V_{\text{gs}} - V_{\text{t}})/m$  [Eq. (6.6.5)]. It is smaller than the latter. Note that  $\mathscr{C}_{\text{sat}}$  is defined with Eq. (6.9.8).<sup>5</sup> It is known that  $v_{\text{sat}}$  is  $8 \times 10^6$  cm/s for electrons and  $6 \times 10^6$  cm/s for holes.

#### **EXAMPLE 6–2 Drain Saturation Voltage**

At  $V_{gs} = 1.8$  V, what is the  $V_{dsat}$  of an NMOSFET with  $T_{oxe} = 3$  nm,  $V_t = 0.25$  V, and  $W_{dmax} = 45$  nm for (a)  $L = 10 \mu$ m, (b)  $L = 1 \mu$ m, (c)  $L = 0.1 \mu$ m, and (d)  $L = 0.05 \mu$ m?

#### SOLUTION:

From Fig. 6–9 or Eq. (6.3.7),  $\mu_n$  is 200 cm<sup>2</sup>/V/s. Using Eq. (6.9.8)

$$\mathscr{C}_{sat} = 2v_{sat}/\mu_{ns} = 2 \times 8 \times 10^6 \text{ cm/s} \div 200 \text{ cm}^2/\text{Vs} = 8 \times 10^4 \text{ V/cm}$$

Using Eq. (6.5.2)

$$m = 1 + 3T_{\text{oxe}}/W_{\text{dmax}} = 1 + 9 \text{ nm}/45 \text{ nm} = 1.2$$

Using Eq. (6.9.10)

$$V_{\rm dsat} = \left(\frac{m}{V_{\rm gs} - V_{\rm t}} + \frac{1}{\mathcal{E}_{\rm sat}L}\right)^{-1}$$

**a.**  $L = 10 \,\mu\text{m}$ ,

$$V_{\text{dsat}} = \left(\frac{1.2}{1.55 \text{ V}} + \frac{1}{8 \times 10^4 \text{ V/cm} \cdot L}\right)^{-1} = \left(\frac{1}{1.3 \text{ V}} + \frac{1}{80 \text{ V}}\right)^{-1} = 1.3 \text{ V}$$

**b.**  $L = 1 \,\mu m$ ,

$$V_{\rm dsat} = \left(\frac{1}{1.3\,\rm V} + \frac{1}{8\,\rm V}\right)^{-1} = 1.1\,\rm V$$

**c.**  $L = 0.1 \,\mu\text{m}$

$$V_{\rm dsat} = \left(\frac{1}{1.3\,\rm V} + \frac{1}{0.8\,\rm V}\right)^{-1} = 0.5\,\rm V$$

**d.**  $L = 0.05 \,\mu\text{m}$

$$V_{\rm dsat} = \left(\frac{1}{1.3 \,\rm V} + \frac{1}{0.4 \,\rm V}\right)^{-1} = 0.3 \,\rm V$$

Clearly, short-channel  $V_{dsat}$  is much smaller than long-channel  $V_{dsat}$ ,  $V_g - V_t$ .

Substituting Eq. (6.9.10) for  $V_{ds}$  in Eq. (6.9.3)

$$I_{\rm dsat} = \frac{W}{2mL} C_{\rm oxe} \mu_{ns} \frac{\left(V_{\rm gs} - V_{\rm t}\right)^2}{1 + \frac{V_{\rm gs} - V_{\rm t}}{m\mathfrak{E}_{\rm sat}L}} = \frac{\text{long channel } I_{\rm dsat} (\rm Eq. \, (6.6.6))}{1 + \frac{V_{\rm gs} - V_{\rm t}}{m\mathfrak{E}_{\rm sat}L}}$$

(6.9.11)

<sup>&</sup>lt;sup>5</sup> You may find this  $\mathscr{E}_{sat}$  definition to be inconsistent with Eq. (6.8.1). Equations (6.9.6)–(6.9.8) match the sharp curvature and the asymptotic values of the velocity-field data better than Eq. (6.8.6) [9].

Two special cases of Eqs. (6.9.10) and (6.9.11) are discussed below.

1. Long-channel or low  $V_{gs}$  case,  $\mathscr{E}_{sat}L >> V_{gs} - V_t$

$$V_{\rm dsat} = (V_{\rm gs} - V_{\rm t})/m$$

(6.9.12a)

$$I_{\rm dsat} = \frac{W}{2mL} C_{\rm oxe} \mu_{ns} (V_{\rm gs} - V_{\rm t})^2$$

(6.9.12b)

These are identical to Eqs. (6.6.5) and (6.6.6). The long-channel model is valid when L is large.

#### How Large Must L Be to Be "Long Channel"?

The condition  $\mathscr{E}_{sat}L >> V_{gs} - V_t$  can be satisfied when L is large or when  $V_{gs}$  is close to  $V_t$ . The latter case is frequently encountered in analog circuits where the gate is biased close to  $V_t$  to reduce power consumption. Assuming  $\mathscr{E}_{sat} = 6 \times 10^4$  V/cm and  $V_{gs}$   $V_t = 2$  V (for digital circuits), a 0.2 µm channel length would not satisfy the condition of  $\mathscr{E}_{sat}L >> V_{gs} - V_t$ . Therefore, it exhibits significant short-channel behaviors. But, read on. If  $V_{gs} - V_t = 0.1$  V (for low-power analog circuits), even a 0.1 µm channel length would satisfy the inequality and the transistor would exhibit some *long-channel* characteristics, i.e.,  $I_{dsat} \propto (V_{gs} - V_t)^2/L$  and  $V_{dsat} = (V_{gs} - V_t)/m$ . For applications to this low-power analog circuit, the "long-channel" equations such as Eq. (6.6.6) may be used even if L is 0.05 µm.

There are other short-channel behaviors that are observable even at small  $V_{gs} - V_t$ , e.g., a larger leakage current and a larger slope in the  $I_d - V_d$  plot at  $V_{ds} > V_{dsat}$ . These other behaviors are sensitive to transistor design parameters such as  $T_{oxe}$  as explained in the next chapter.

2. Very short-channel case,  $\mathscr{E}_{sat}L \ll V_{gs} - V_t$

$$V_{\rm dsat} \approx \mathscr{C}_{\rm sat} L < \frac{(V_{\rm g} - V_{\rm t})}{m}$$

(6.9.13)

$$I_{\rm dsat} \approx W v_{\rm sat} C_{\rm oxe} (V_{\rm gs} - V_{\rm t} - m \mathscr{E}_{\rm sat} L) \tag{6.9.14}$$

$I_{\text{dsat}}$  is proportional to  $V_{\text{gs}} - V_t$  rather than  $(V_{\text{gs}} - V_t)^2$  and is less sensitive to L than the long-channel  $I_{\text{dsat}}$  ( $\approx 1/L$ ). Equation (6.9.14), derived from Eq. (6.9.11) by Taylor expansion, is quite easy to understand.  $I_{\text{dsat}}$  is proportional to W. Carriers travel at the saturation velocity at the drain end of the channel where  $Q_{\text{inv}} = C_{\text{oxe}}(V_{\text{gs}} - V_t - mV_{\text{dsat}})$  and  $V_{\text{dsat}}$  is  $\mathscr{E}_{\text{sat}}L$ .

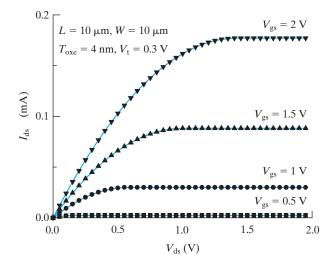

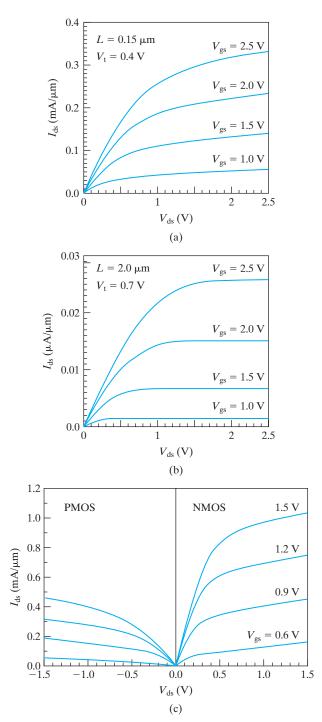

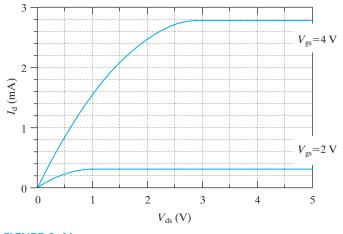

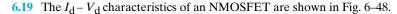

Figure 6–23a and b compare the measured IV characteristics of two NFETs with  $L = 0.15 \,\mu\text{m}$  and  $L = 2 \,\mu\text{m}$ . The shorter channel device shows an approximately linear relationship between  $I_{\text{dsat}}$  and  $V_{\text{gs}}$  in agreement with Eq. (6.9.14).  $V_{\text{dsat}}$  is significantly less than  $(V_{\text{gs}} - V_{\text{t}})/m$ . (The behavior at  $V_{\text{ds}} > V_{\text{dsat}}$  is explained in Sec. 7.9.) The 2  $\mu$ m channel device shows a superlinear increase of  $I_{\text{dsat}}$  with increasing  $V_{\text{g}}$  in rough agreement with Eq. (6.9.12).

To raise  $I_{dsat}$ , we must increase  $C_{oxe}(V_{gs} - V_t)$ , i.e., reduce  $T_{oxe}$ , minimize  $V_t$ , and use high  $V_{gs}$  The limit of  $T_{oxe}$  is set by oxide tunneling leakage and reliability. The lower limit of  $V_t$  is set by MOSFET leakage in the off state. These will be discussed in the next chapter. The maximum  $V_{gs}$  is the power supply voltage,  $V_{dd}$ , which is limited by concerns over circuit power consumption and device reliability.

•

**FIGURE 6–23 Measured IV characteristics.** (a) A 0.15 µm channel device ( $V_t = 0.4$  V) shows a linear relationship between  $I_{dsat}$  and  $V_{gs}$ .  $V_{dsat}$  is significantly less than  $V_{gs} - V_t$ . (b) A 2 µm device ( $V_t = 0.7$  V) exhibits the  $I_{dsat} \propto (V_{gs} - V_t)^2$  relationship. (c) IV characteristics of PFET and NFET with  $T_{oxe} = 3$  nm and  $L \approx 100$  nm.

Figure 6–23c shows that PFET and NFET have similar IV characteristics, e.g., both exhibit a linear  $I_{dsat}-V_g$  relationship.  $I_P$  is about half of  $I_N$ . The holes' mobility is three times smaller and their saturation velocity is 30% smaller than that of the electrons.

#### 6.9.1 Velocity Saturation vs. Pinch-Off

The concept of pinch-off in Section 6.6 suggests that  $I_{ds}$  saturates when  $Q_{inv}$  becomes zero at the drain end of the channel. A more accurate description of the cause of current saturation is that the carrier velocity has reached  $v_{sat}$  at the drain. Instead of the pinch-off region, there is a **velocity saturation region** next to the drain where  $Q_{inv}$  is a constant  $(I_{dsat}/W_{vsat})$ . The series of plots in Fig. 6–17 are still valid with one modification. In (b) and (f),  $Q_{inv} = I_{dsat}/W_{vsat}$  at L. In (f), of course, there is a very short region next to L, the velocity saturation region, where  $Q_{inv}$  remains constant. This region is not shown in Fig. 6–17 for simplicity.

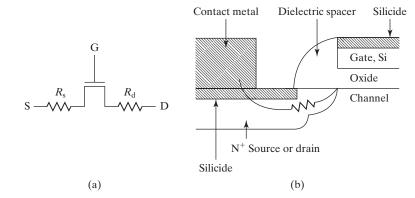

#### 6.10 • PARASITIC SOURCE-DRAIN RESISTANCE •

The main effect of the parasitic resistance shown in Fig. 6–24a is that  $V_{gs}$  in the  $I_{ds}$  equations is reduced by  $R_s \cdot I_{ds}$ . For example, Eq. (6.9.14) becomes

$$I_{\rm dsat} = \frac{I_{\rm dsat0}}{1 + R_{\rm s} I_{\rm dsat0} / (V_{\rm gs} - V_{\rm t})}$$

(6.10.1)

$I_{\text{dsat0}}$  is the current in the absence of  $R_{\text{s}}$ .  $I_{\text{dsat}}$  may be significantly reduced by the parasitic resistance, and the impact is expected to rise in the future. The shallow diffusion region under the dielectric spacer is a contributor to the parasitic resistance. The shallow junction is needed to prevent excessive off-state leakage  $I_{\text{ds}}$  in short-channel transistors (see Section 7.6). The silicide (e.g., TiSi<sub>2</sub> or NiSi<sub>2</sub>) reduces the **sheet resistivity**<sup>6</sup> of the N<sup>+</sup> (or P<sup>+</sup>) source–drain regions by a factor of ten. It also reduces the

#### **FIGURE 6–24** Source–drain series resistance.

<sup>6</sup> If the sheet resistivity of a film is 1  $\Omega$  per square, the resistance between two opposite edges of a squareshaped piece of this film (regardless of the size of the square) will be 1  $\Omega$ .

**contact resistance** between the silicide and the N<sup>+</sup> or P<sup>+</sup> Si. The contact resistance is another main source of resistance and more on this subject may be found in Section 4.21. The dielectric spacer is produced by coating the structure in Fig. 5–1 with a conformal film of dielectric followed by anisotropic dry etching to remove the dielectric from the horizontal surfaces. The silicides over the source/drain diffusion regions and over the gate are formed simultaneously by reaction between metal and silicon at a high temperature. The unreacted metal over the surface of the dielectric spacer is removed with acid. A second effect of the series resistance is an increase in  $V_{dsat}$ :

$$V_{\rm dsat} = V_{\rm sat0} + I_{\rm dsat}(R_{\rm s} + R_{\rm d})$$

(6.10.2)

where  $V_{dsat0}$  is the  $V_{dsat}$  in the absence of  $R_s$  and  $R_d$ .

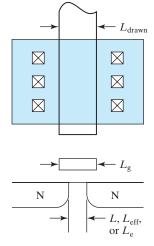

### 6.11 • EXTRACTION OF THE SERIES RESISTANCE AND THE EFFECTIVE CHANNEL LENGTH<sup>7</sup> •

Figure 6–25 illustrates the channel length and two other related quantities. A circuit designer specifies a channel length in the circuit layout, called the drawn gate length,  $L_{drawn}$ . This layout is transferred to a photomask, then to a photoresist pattern, and finally to the physical gate. The final physical **gate length**,  $L_g$ , may not be equal to  $L_{drawn}$  because each pattern transfer can introduce some dimensional change. However, engineers devote extraordinary efforts, e.g., by OPC (optical proximity correction) (see Section 3.3) to minimize the difference between  $L_{drawn}$  and  $L_g$ . As a result, one may assume  $L_{drawn}$  and  $L_g$  to be equal.  $L_g$  can be measured using scanning electron microscopy (SEM).

For device analysis and modeling, it is necessary to know the channel length, L, also called the effective channel length  $(L_{eff})$  or the electrical channel length  $(L_e)$  to differentiate it from  $L_{drawn}$  and  $L_g$ . It is particularly useful to know the

**FIGURE 6–25**  $L_{\text{drawn}}$ ,  $L_{\text{g}}$ , and L (also known as  $L_{\text{eff}}$  or  $L_{\text{e}}$ ) are different in general.

<sup>&</sup>lt;sup>7</sup> This section may be omitted in an accelerated course.

#### 6.11 • Extraction of the Series Resistance and the Effective Channel Length

difference between  $L_{drawn}$  and L. This difference is called  $\Delta L$ , which is assumed to be a constant, independent of  $L_{drawn}$

$$L = L_{\rm drawn} - \Delta L \tag{6.11.1}$$

Measuring  $\Delta L$  in short transistors is quite difficult. There are several imperfect options. The following method is the oldest and still commonly used. From Eq. (6.3.1),

$$V_{\rm ds} = \frac{I_{\rm ds}(L_{\rm drawn} - \Delta L)}{WC_{\rm oxe}(V_{\rm gs} - V_{\rm t})\mu_{ns}}$$

(6.11.2)

When the series resistance,  $R_{\rm ds} \equiv R_{\rm d} + R_{\rm s}$ , shown is Fig. 6–24a is included, Eq. (6.11.2) becomes

$$V_{\rm ds} = I_{\rm ds} R_{\rm ds} + \frac{I_{\rm ds} (L_{\rm drawn} - \Delta L)}{W C_{\rm oxe} (V_{\rm gs} - V_{\rm t}) \mu_{ns}}$$

(6.11.3)

$$\frac{V_{\rm ds}}{I_{\rm ds}} (= R_{\rm ds} + \text{channel resistance}) = R_{\rm ds} + \frac{L_{\rm drawn} - \Delta L}{WC_{\rm oxe}(V_{\rm gs} - V_{\rm t})\mu_{ns}}$$

(6.11.4)

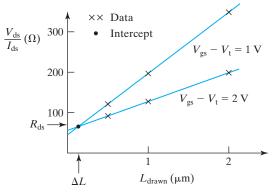

Figure 6–26 plots the measured  $V_{\rm ds}/I_{\rm ds}$  against  $L_{\rm drawn}$  using three MOSFETs that are identical (fabricated on the same test chip) except for their  $L_{\rm drawn}$ s.  $I_{\rm ds}$  is measured at a small  $V_{\rm ds}$  ( $\leq 50$  mV) and at least two values of  $V_{\rm gs} - V_{\rm t}$ .  $V_{\rm ds}/I_{\rm ds}$  is a linear function of  $L_{\rm drawn}$ . The two straight lines intersect at a point where  $V_{\rm ds}/I_{\rm ds}$  is independent of  $V_{\rm gs} - V_{\rm t}$  according to Eq. (6.11.4), i.e., where  $L_{\rm drawn} = \Delta L$  and  $V_{\rm ds}/I_{\rm ds} = R_{\rm ds}$ . Once  $\Delta L$  is known, L can be calculated using Eq. (6.11.1).

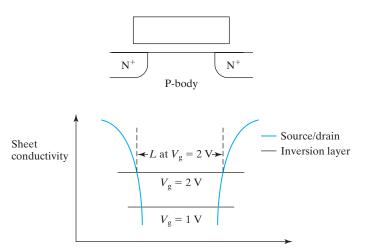

Detailed measurements indicate that  $R_{ds}$  tends to decrease with increasing  $V_g$ . One reason is that the gate voltage induces more (accumulation) electrons in the source-drain diffusion region and therefore reduces  $R_{ds}$ . More puzzling is the observation that  $\Delta L$  decreases (or L increases) with increasing  $V_g$ . The dependence of both  $\Delta L$  and  $R_{ds}$  on  $V_g$  suggests the interpretation of channel length illustrated in Fig. 6–27 [10]. The sheet conductivities (inverse of sheet resistivity, introduced in Section 6.10) of the source-drain diffusion regions and the channel inversion layer (the horizontal lines) are plotted. The inversion-layer sheet conductivity increases with increasing  $V_g$ , of course. The channel length may be interpreted as the length of the part of the channel where the inversion-layer sheet conductivity is larger than the source/drain sheet conductivity. In other words, the channel is where the

**FIGURE 6–26** Method of extracting  $R_{ds}$  and  $\Delta L$ .

**FIGURE 6–27** Interpretation of channel length and its dependence on  $V_{g}$ .

conductivity is determined by  $V_{\rm g}$ , not by the source–drain doping profiles. Any resistance from outside the "channel" is attributed to  $R_{\rm ds}$ . It is clear from Fig. 6–27 that the channel expands (i.e., *L* increases and  $R_{\rm ds}$  decreases) with increasing  $V_{\rm g}$ .

### 6.12 • VELOCITY OVERSHOOT AND SOURCE VELOCITY LIMIT<sup>8</sup> •

The concept of mobility is dubious when the channel length is comparable to or smaller than the mean free path (see Section 2.2.2). For this reason, Eq. (6.9.14) is particularly interesting because it does not contain mobility. The carrier velocity at the drain end of the channel is limited by the saturation velocity, which determines  $I_{dsat}$ . However, when the channel length is reduced much below 100 nm, the saturation velocity may be greatly raised by velocity overshoot as explained in Section 6.8. In that case, some other limit on  $I_{dsat}$  may set in.

The carrier velocity at the source becomes the limiting factor. There, the velocity is limited by the thermal velocity, with which the carriers enter the channel from the source. This is known as the **source injection velocity** limit.

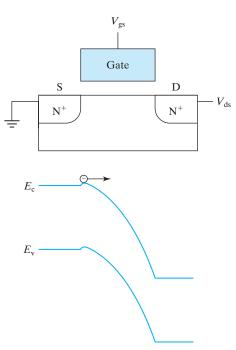

The source is a reservoir of carriers moving at the thermal velocity. As the channel length approaches zero, all the carriers moving from the source into the channel are captured by the drain. No carriers flow from the drain to the source due to the voltage difference (or energy barrier) shown in Fig. 6–28.

$$I_{dsat} = WBv_{thx}Q_{inv} = WBv_{thx}C_{oxe}(V_{gs} - V_t)$$

(6.12.1)

Equation (6.12.1) is similar to Eq. (6.9.14) except that  $v_{sat}$  is replaced by  $v_{thx}$ , the *x*-direction component of the thermal velocity. Thorough analysis of  $v_{thx}$  shows that  $v_{thx}$  is about  $1.6 \times 10^7$  cm/s for electrons and  $1 \times 10^7$  cm/s for holes in silicon MOSFETs [11]. *B* is the fraction of carriers captured by the drain in a real transistor. The rest of the injected carriers are scattered back toward the source.

<sup>&</sup>lt;sup>8</sup> This section may be omitted in an accelerated course.

#### 6.13 • Output Conductance

**FIGURE 6–28** In the limit of no scattering in a very short channel, carriers are injected from the source into the channel at the thermal velocity and travel ballistically to the drain.

A particle simulation technique called the Monte Carlo simulation arrived at 0.5 as a typical value of *B* [11]. This makes Eq. (6.12.1) practically identical to Eq. (6.9.14) because  $v_{sat}$  is about  $8 \times 10^6$  cm/s for electrons and  $6 \times 10^6$  cm/s for holes. Both the drain-end velocity saturation limit and the source-end injection velocity limit predict similar  $I_{dsat}$ . *B* in Eq. (6.12.1) is expected to increase somewhat with decreasing *L* as  $v_{sat}$  in Eq. (6.9.14) is expected to do, too.

#### 6.13 • OUTPUT CONDUCTANCE •

The saturation of  $I_{ds}$  (at  $V_{ds} > V_{dsat}$ ) is rather clear in Fig. 6–23b. The saturation of  $I_{ds}$  in Fig. 6–23a is gradual and incomplete. The cause for the difference is that the channel length is long in the former case and short in the latter. The slope of the I-V curve is called the **output conductance**

$$g_{\rm ds} = \frac{\mathrm{d}I_{\rm dsat}}{\mathrm{d}V_{\rm ds}} \tag{6.13.1}$$

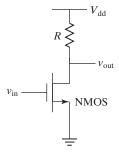

A clear saturation of  $I_{ds}$ , i.e., a small  $g_{ds}$  is desirable. The reason can be explained with the simple amplifier circuit in Fig. 6–29. The bias voltages are chosen such that the transistor operates in the saturation region. A small-signal input,  $v_{in}$ , is applied.

$$i_{\rm ds} = g_{msat} \cdot v_{\rm gs} + g_{\rm ds} \cdot v_{\rm ds} \tag{6.13.2}$$

$$= g_{msat} \cdot v_{in} + g_{ds} \cdot v_{out}$$

$$v_{out} = -R \times i_{ds}$$

(6.13.3)

FIGURE 6–29 A simple MOSFET amplifier.

Eliminate  $i_{ds}$  from the last two equations and we obtain

$$v_{\rm out} = \frac{-g_{msat}}{g_{\rm ds} + 1/R} \times v_{\rm in} \tag{6.13.4}$$

The magnitude of the output voltage, according to Eq. (6.13.4) is amplified from the input voltage by a **gain** factor of  $\frac{g_{msat}}{g_{ds} + 1/R}$ . The gain can be increased by using a large *R*. Even with *R* approaching infinity, the voltage gain cannot exceed

Maximum Voltage Gain =

$$\frac{g_{msat}}{g_{ds}}$$

(6.13.5)

This is the **intrinsic voltage gain** of the transistor. If  $g_{ds}$  is large, the voltage gain will be small. As an extreme example, the maximum gain will be only 1 if  $g_{ds}$  is equal to  $g_{msat}$ . A large gain is obviously beneficial to analog circuit applications. A reasonable large gain is also needed to obtain a steep transition in the VTC, i.e., needed for digital circuit applications to enhance noise immunity. Therefore,  $g_{ds}$  must be kept much lower than  $g_{msat}$ .

The physical causes of the output conductance are the influence of  $V_{\rm ds}$  on  $V_{\rm t}$ and a phenomenon called channel length modulation. They are discussed in Section 7.9. The conclusions may be summed up this way. In order to achieve a small  $g_{\rm ds}$  and a large voltage gain, L should be large and/or  $T_{\rm ox}$ ,  $W_{\rm dep}$ , and  $X_j$ should be small.

#### 6.14 • HIGH-FREQUENCY PERFORMANCE •

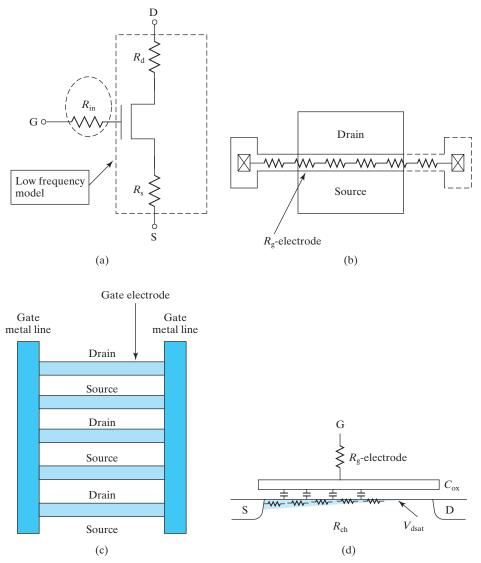

The high-frequency performance of the MOSFET shown in Fig. 6–30a is limited by the input RC time constant. *C* is the gate capacitance,  $C_{ox}WL_g$ . At high frequencies, the gate capacitive impedance,  $1/2\pi fC$ , decreases and the gate AC current increases. More of the gate signal voltage is dropped across  $R_{in}$ , and the output current is reduced. At some high frequency, the output current becomes equal to the input current. This unit current-gain frequency is called the *cutoff frequency*,  $f_T$ . In narrow-band analog circuits operating at a particular high frequency, the gate capacitance may be compensated with an on-chip inductor at that frequency to

**FIGURE 6–30** (a) The input resistance together with the input capacitance sets the high-frequency limit. (b) One component of  $R_{in}$  is the gate-electrode resistance. (c) The multi-finger layout dramatically reduces the gate-electrode resistance. (d) The more fundamental and important component of  $R_{in}$  is the channel resistance, which is also in series with the gate capacitor.

overcome the  $f_T$  limit. In that case,  $R_{in}$  still consumes power and at some frequency, typically somewhat higher than  $f_T$ , the power gain drops to unity. This frequency is called the **maximum oscillation frequency**,  $f_{max}$ . In either case, it is important to minimize  $R_{in}$ .

$R_{\rm in}$  consists of two components, the **gate-electrode resistance**,  $R_{\rm g-electrode}$ , and the **intrinsic input resistance**,  $R_{\rm ii}$ .

$$R_{\rm in} = R_{\rm g-electrode} + R_{\rm ii} \tag{6.14.1}$$

The gate-electrode resistance is straightforward as shown in Fig. 6–30b. A powerful way to reduce the gate-electrode resistance is **multi-finger layout** shown in Fig. 6–30c, which means designing a MOSFET with a large channel width, say 10  $\mu$ m, as 10 MOSFETs connected in parallel each having a width of 1  $\mu$ m. This reduces the gate-electrode resistance by a factor of 100 because each finger's resistance is ten times smaller and there are now ten finger resistors in parallel.

$$R_{g-\text{electrode}} = \rho W / 12 T_g L_g N_{f2} \tag{6.14.2}$$

$\rho$  is the gate resistivity of the gate material, *W*, is the total channel width,  $T_g$  is the gate thickness,  $L_g$  is the gate length, and  $N_f$  is the number of fingers. The factor 12 comes from two sources. A factor of three comes from the fact that the gate current is distributed over the finger width and all the gate capacitor current does not flow through the entire finger resistor. The remaining factor of four arises from contacting the gate fingers at both the left and the right ends of the fingers as shown in Fig. 6–30c. Doing so effectively doubles the number of fingers and halves the finger width as if each finger is further divided into two at the middle of the finger. Using multifinger layout, the gate-electrode resistance can be quite low if the gate material is silicided poly-silicon. If the gate material is metal, this component of  $R_{in}$ becomes negligible.

The more important, fundamental, and interesting component is the intrinsic input resistance. The concept is illustrated in Fig. 6–30d. Even if  $R_{g-electrode}$  is zero, there is still a resistor in series with the gate capacitor. The gate capacitor current flows through the channel resistance,  $R_{ch}$ , to the source, then through the input signal source (not shown) back to the gate to complete the current loop.  $R_{ii}$  is a resistance in the path of the gate current[12].

$$R_{\rm ii} = \kappa \int dR_{\rm ch} = \kappa \frac{V_{\rm ds}}{I_{\rm ds}}$$

(6.14.3)

k is a number smaller than one [12] because due to the distributed nature of the RC network in Fig. 6–30d, the capacitance current does not flow through the entire channel resistance.  $V_{ds}$  Eq. (6.14.3) saturates at  $V_{dsat}$  when  $V_{ds} > V_{dsat}$ .

With each new generation of MOSFET technology, the gate length is reduced making  $R_{ii}$  smaller for a fixed W due to larger  $I_{ds}$  and smaller  $V_{dsat}$ . Furthermore, the input capacitance  $C_{ox}WL_g$  is reduced somewhat when  $L_g$  is made smaller although  $C_{ox}$  is made larger ( $T_{oxe}$  thinner) at the same time. As a result,  $f_T$  and  $f_{max}$  have been improving linearly with the gate length. They are about 200 GHz in the 45 nm technology node, sufficient for a wide range of new applications.

# 6.15 MOSFET NOISES

**Noise** is whatever that corrupts the desired signal. One type of noise, the inductive and capacitive interferences or **cross talk** created by the interconnect network, may be called external noise. This kind of noise is important but can be reduced in principle by careful shielding and isolation by the circuit designers. The other noise category is called **device noise** that is inherent to the electronic devices. This kind of noise is due to the random behaviors of the electric carriers inside the device that create voltage and current fluctuations measurable at the terminals of the device. This section is concerned with the device noise. *Noise, power consumption, speed, and circuit size (cost) are the major circuit-design constraints.*

# 6.15.1 Thermal Noise of a Resistor

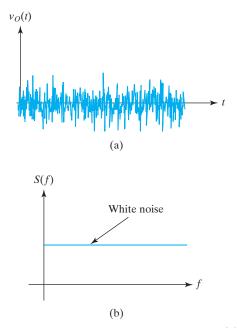

If a resistor is connected to the input of an oscilloscope, the noise voltage across the resistor can be observed as shown in Fig. 6–31a. The origin of the noise is the random thermal motion of the charge carriers shown in Fig. 2–1, and the noise is called the **thermal noise**. The noise contains many frequency components. If one inserts a frequency filter with bandwidth  $\Delta f$  and measures the root-mean-square value of the noise in this frequency band, the results are

$$v_n^2 = S_{v_n} \Delta f = 4k T \Delta f R$$

(6.15.1)

$$i_n^2 = \mathbf{S}_{\mathbf{i}_n} \Delta f = 4\mathbf{k} \mathbf{T} \Delta f / R \tag{6.15.2}$$

where R is the resistance and Eq. (6.15.2) presents the noise current that would flow if the resistor's terminals were short-circuited. Clearly, the noise is proportional to  $\Delta f$  but is independent of f. This characteristic is called **white noise** and its **noise spectral density** is shown in Fig. 6–31b. S is called the noise power density.

# 6.15.2 MOSFET Thermal Noise

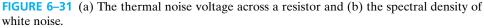

The intrinsic thermal noise of MOSFETs originates from the channel resistance. The channel may be divided into many segments as shown in Fig. 6–32 and each contributes some noise. The channel noise voltage can be expressed by Eq. (6.15.1).

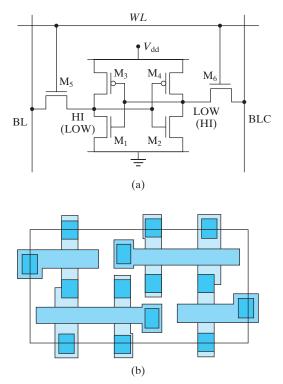

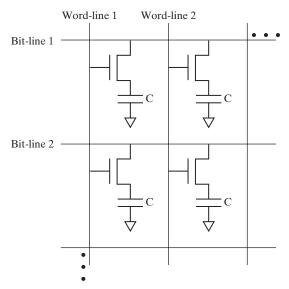

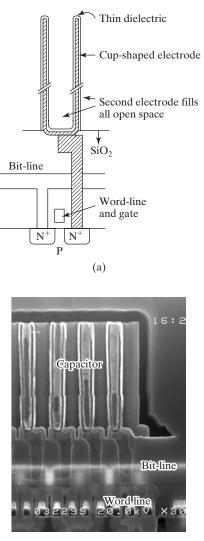

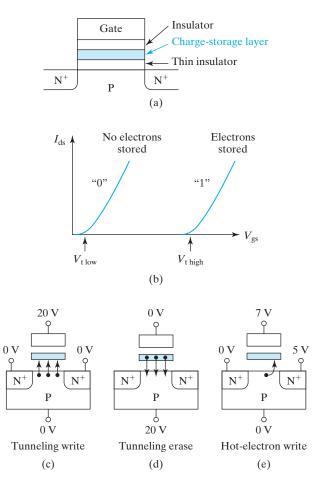

**FIGURE 6–32** (a) Each segment of the channel may be considered a resistor that contributes thermal noise. (b) The noise current is added to the normal MOSFET current as a parallel current source. The noise voltage is multiplied by the transconductance into another component of noise current. (c) Parasitic resistances also contribute to the thermal noises.